Verilog HDL 通过示例

价格: $19.99

嘿, 欢迎大家参加我的课程‘Verilog HDL through Examples’

为什么选择 Verilog?

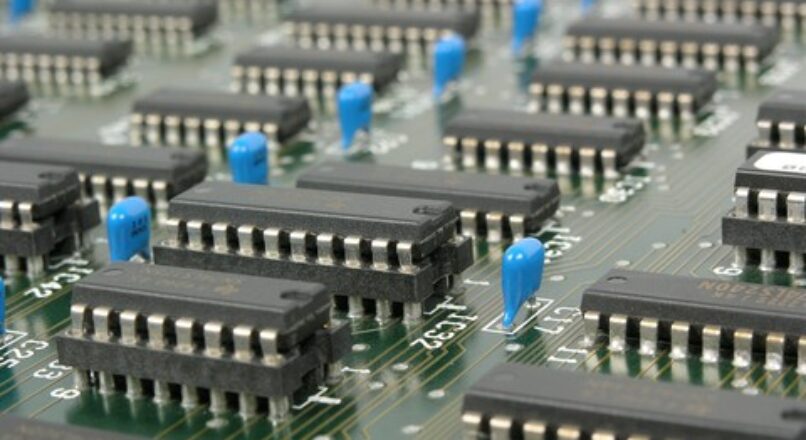

1. 描述任何数字系统 – 微处理器, 记忆, 拖鞋, 使用 Verilog. 因此它被称为硬件描述语言.

2. 使用 Verilog, 我们可以对任何电子元件进行建模并为其生成原理图.

3. 用于电路的时序分析和测试分析, Verilog 很合适.

课程亮点:

1. 像 C 这样的编程语言之间的主要区别, C++ 或 Python 以及像 Verilog 这样的硬件描述语言, 高密度脂蛋白, SystemVerilog 很清楚

2. Verilog 的所有基本概念都通过标准组合电路和时序电路进行了解释.

3. 通过示例学习使它们学习起来非常简单.

4. 为本课程中用verilog实现的每个电路提供了适当的理论解释.

5. 每个设计的测试台,并知道如何测试和验证它们.

6. 在 Verilog 中创建有限状态机.

7. 下载资源部分中每个电路的代码和设计.

8. 了解如何使用 EDA Playground 进行 Verilog 编码以及如何使用 EPWave 生成输出波形.

9. Verilog 的一些关键概念,例如

抽象级别, 两种类型的任务, 产生延迟, 生成时钟, 程序任务都解释清楚.

发表评论

你必须 登录 要么 寄存器 添加新评论 .